این گزارش نهایی در مورد پروژه IOTA Crypto Core است. در صورتی که بخش قبلی را از دست داده اید می توانید به این لینک مراجعه کنید. ۹ ماه جالب از کار کردن در حال به اتمام رسیدن است و حال زمان خلاصه کردن و جمع بندی همه چیز است.

بررسی کلی پروژه IOTA Crypto Core

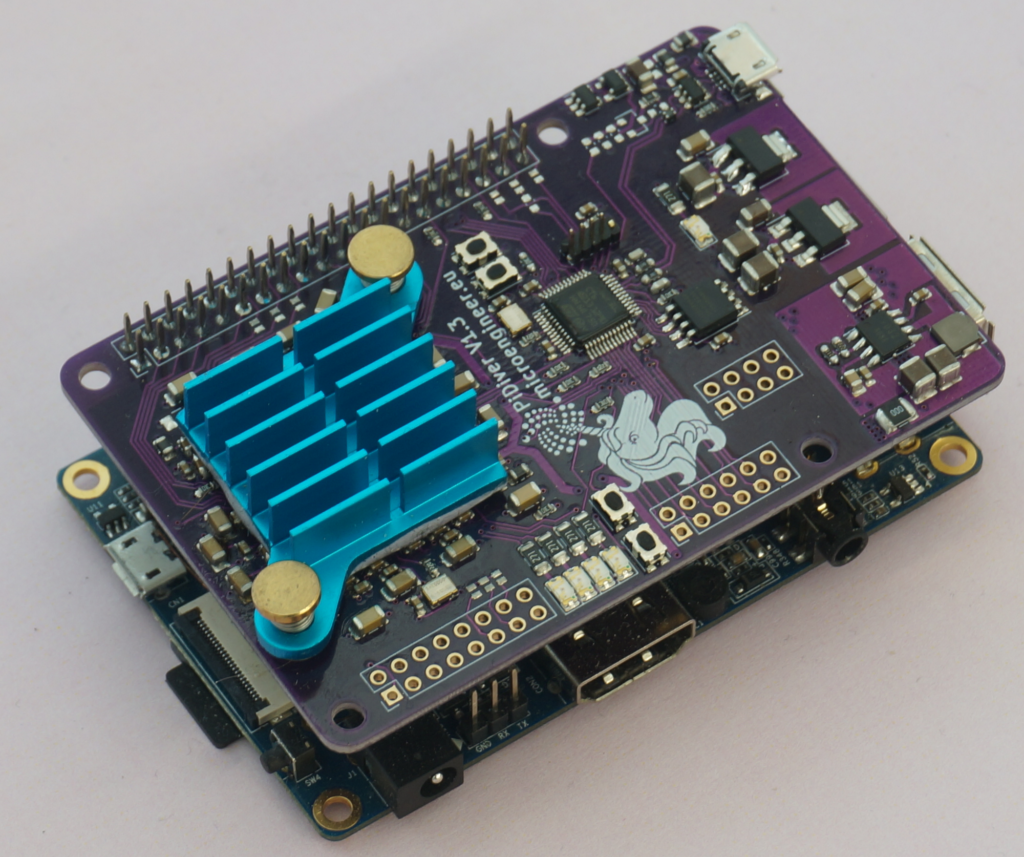

PiDiver PoW

اولین نقطه عطف PiDiver بود. این کار قبل از اینکه تامین وجه اکوسیستم اعلام شود، انجام شده بود و خوشحالم که می توانم آن را در پروپوزال داخل کنم که این پاداش خوبی برای کاری بود که من انجام دادم.

همچنین Powsrv وجود دارد که یک سرویس PoW-as-a-service برای برون سپاری گواه اثبات کار (PoW) به سخت افزار بسیار تخصصی و کالا بر اساس PiDiver می باشد.

IOTA Crypto FPGA Core

دومین نقطه عطف توسعه یک FPGA core بود که اکثر عملکرد های IOTA Crypto Core را با تسریع سخت افزاری فراهم می کند. آن یک API سطح بالا را ارائه می دهد که برای استفاده آسان می باشد و این در حالی است که محاسبات سطح پایین شدید به یک لوجیک تخصصی تخلیه می شود که این مزیت برجسته ای را در سرعت به نسبت یک راه حل تنها نرم افزاری ایجاد می کند.

برای این کار از یک بورد Arty S7 موجود استفاده شد و یک HAT طراحی شد. این HAT دارای یک المنت ایمن، SPI-Flash که قبلا هرگز مورد استفاده قرار نگرفته بود و یک کنترل کننده اترنت W5500 بر روی بورد بود.

در داخل FPGA، یک Cortex M1 soft-cpu در حال اجرا می باشد که می توان آن را با C یا C++ برنامه نویسی کرد. این سفت افزار توسط مکانیسم های امنیتی که FPGA فراهم می کند، محافظت می شود. باید برای مهاجمان سخت باشد که بدون اجازه به سید ها که در یک حافظه ایمن ذخیره شده اند دسترسی پیدا کنند و یا اینکه به دستکاری و مداخله در سفت افزار بپردازند.

همچنین در داخل FPGA، لوجیک تخصصی موجود است که هشینگ (Curl-P81 (and PoW), Keccak384 and Troika) و تبدیل نوع (binary<->trinary) را تسریع می کند. این بلوک های لوجیک تخصصی تسریع بخش های سخت افزار نامیده می شوند و در مقایسه با پیاده سازی صرفا نرم افزاری یک تقویت عملکرد خوبی را ایجاد می کنند. آنها اغلب سریعتر از هشینگ در حال اجرا بر روی یک کامپیوتر شخصی سی پی یو با مثلا ۳ گیگاهرتز می باشند.

واحد IOTA Crypto FPGA

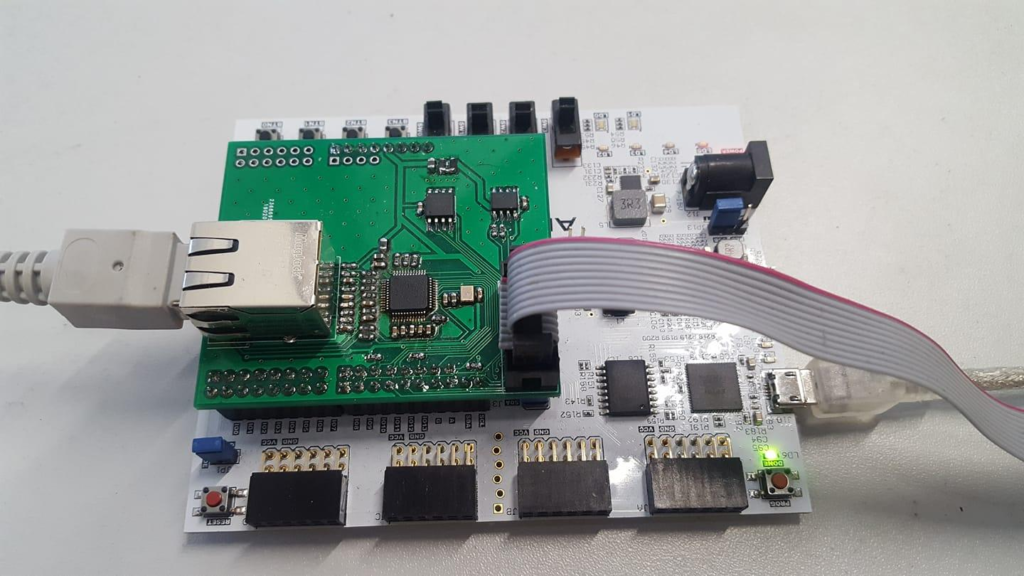

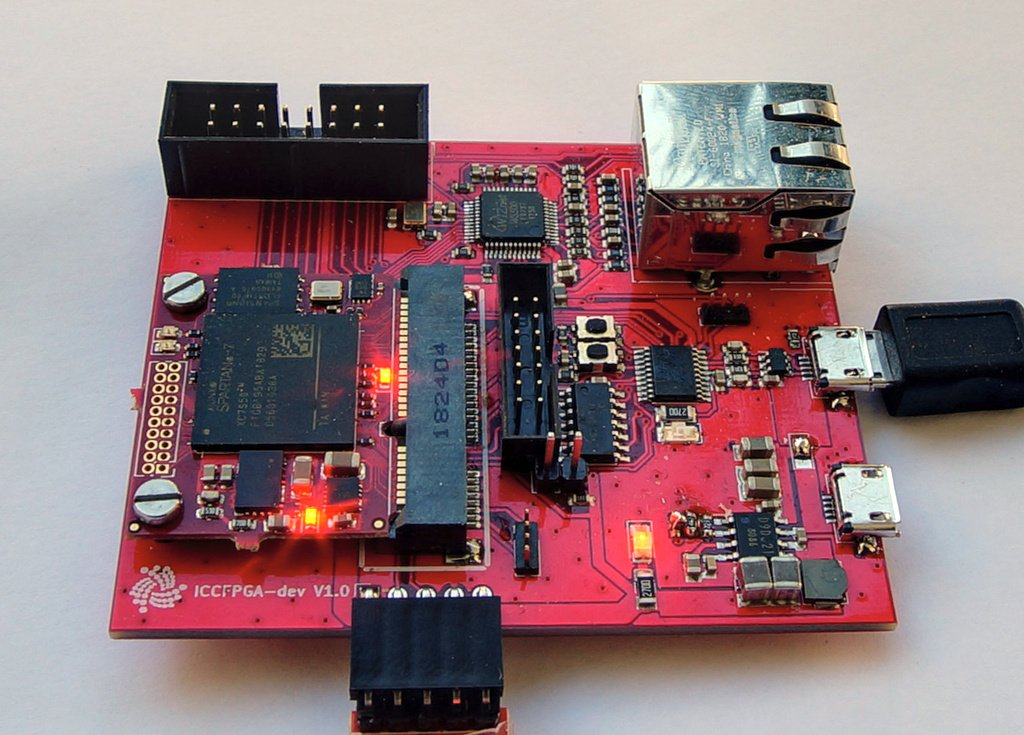

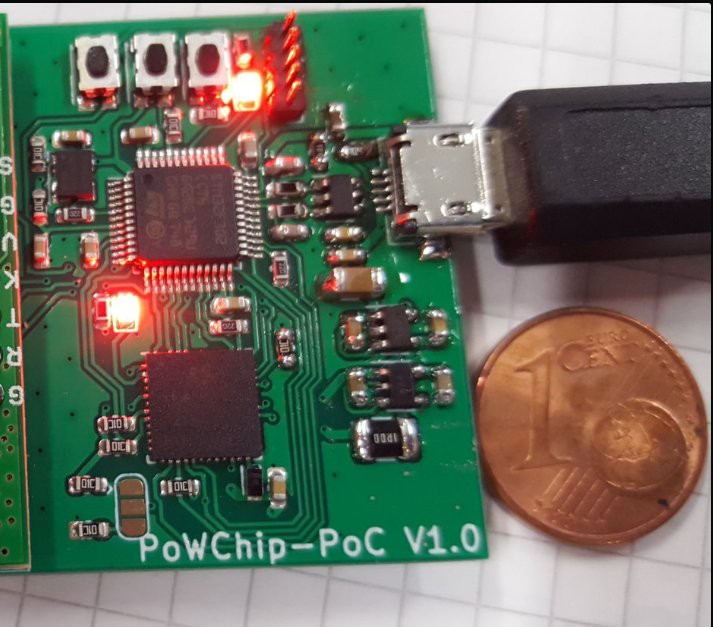

نقطه عطف بعدی ساخت سخت افزار اختصاصی برای FPGA Core بود که در آخرین نقطه عطف توسعه یافت.

نتیجه یک واحد FPGA کوچک بود که می توان آن را در یک سوکت mini-PCIe گذاشت اما آن mini-PCIe نیست.

برای این واحد، همچنین یک بورد تستی کوچک توسعه یافت تا واحد را تست کند.

در ابتدا فکر می کردم که هرگز از این بورد دوباره استفاده نخواهم کرد اما در مورد آن اشتباه می کردم. من آن را دوست دارم و برای هر تغییری از آن استفاده می کنم.

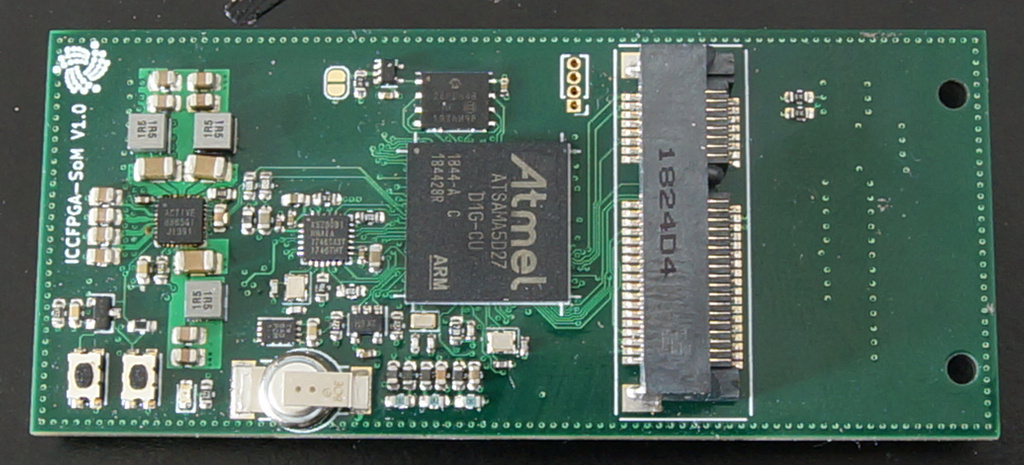

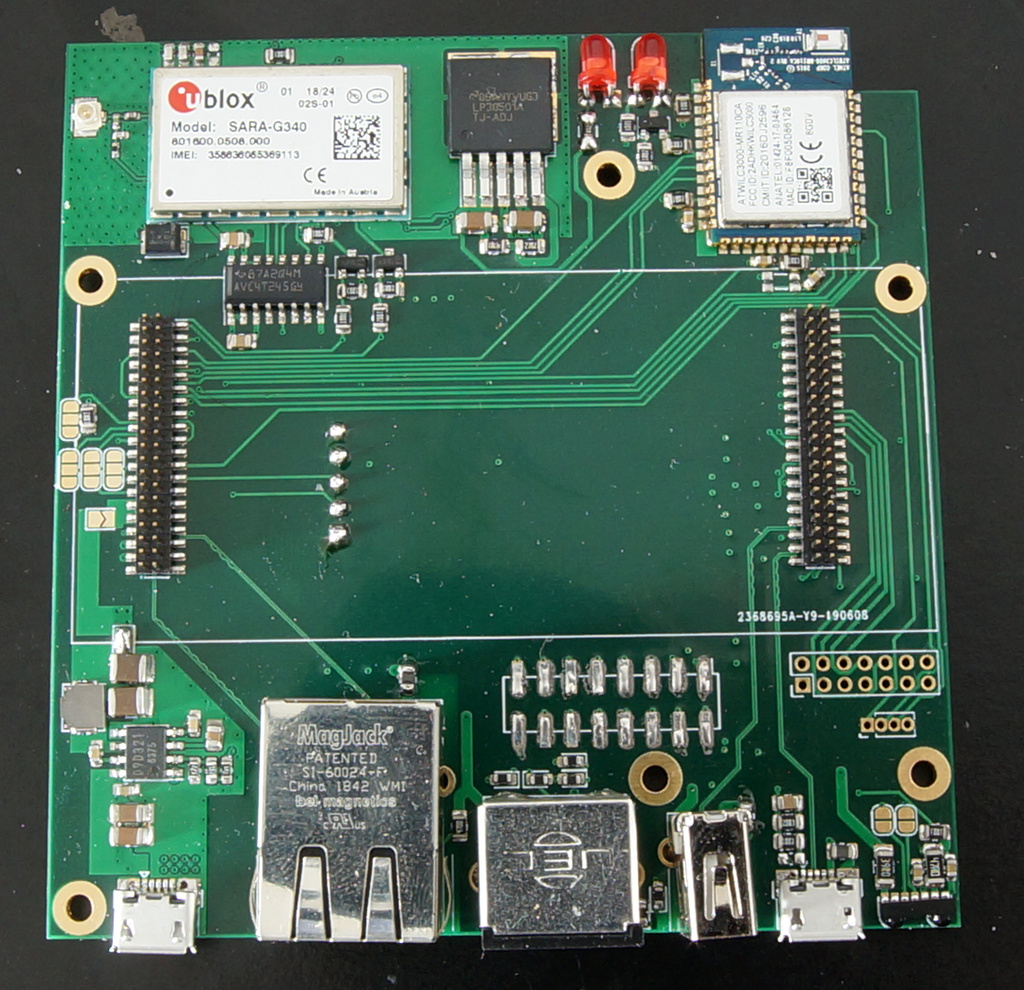

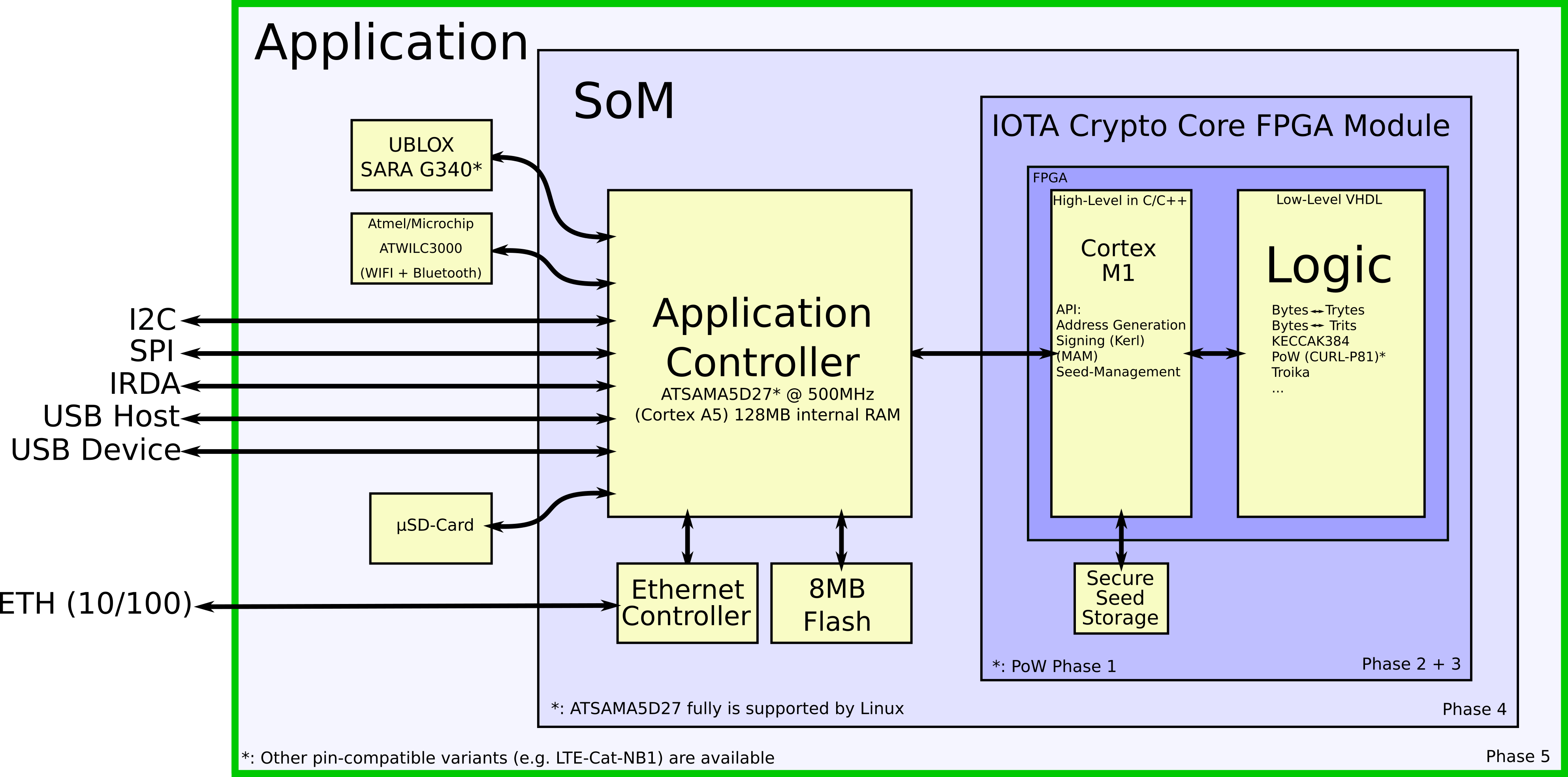

Linux SoM

یک بخش دیگر SoM بود که می توانست از واحد FPGA استفاده کند. در ابتدا یک میکرو کنترل کننده نسبتا بزرگتری برنامه ریزی شده بود اما آن توسط یک میکرو کنترل کننده قدرتمند جایگزین شده بود که دارای قابلیت اجرای لینوکس خط اصلی کامل بود. آن همچنین دارای رم ۱۲۸ مگابایتی می باشد که آن را برای تعداد زیادی از اپلیکیشن ها مناسب می کند.

ATSAMA5D27 دارای ویژگی های امنیتی خیلی خوبی مانند بوت کردن هسته های لینوکسی امضا شده می باشد و آن به قدرت کمی (۱/۲ وات) نیاز دارد. آن همچنین دارای مجموعه خوبی از لوازم جانبی مانند اترنت ۱۰/۱۰۰ Mbit، هاست یو اس بی و دیگر سطح کاربری های سری (I2C، SPI، UART) می باشد.

نقطه عطف ۴، Gateway

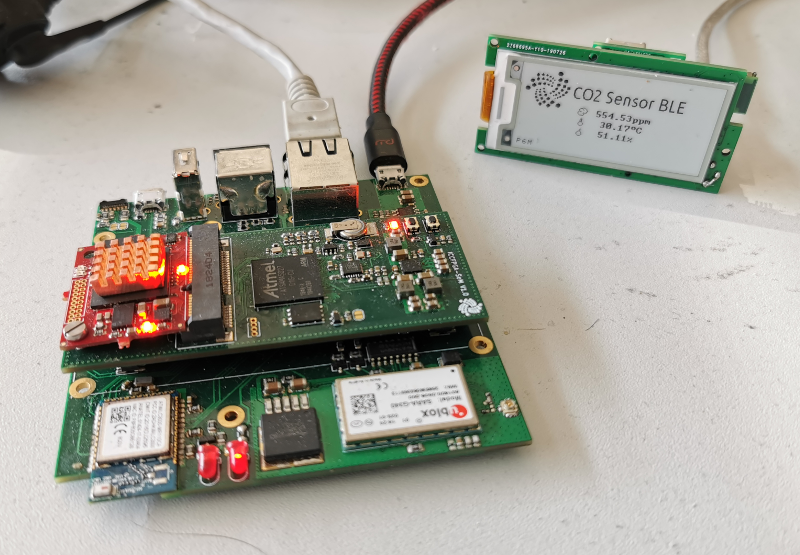

برای استفاده از Linux SoM یک بورد Gateway طراحی شد. آن اکثر لوازم جانبی را در دسترس قرار داد و یک مودم موبایل تری جی، وای فای و بلوتوث را نیز فراهم آورد.

کنار هم گذاشتن همه

در تصویر بالا، سنسور از طریق BLE و low6pan به Gateway متصل شده است و بسته های MQTT را منتشر می کند. نرم افزار اجرا شده بر روی Gateway بر راهنمای MQTT صحه می گذارد و از واحد FPGA برای ساخت کارآمد تراکنش های IOTA Data که سپس به تنگل (tangle) فرستاده می شوند، استفاده می کند.

پروژه های جانبی

تعدادی پروژه های جانبی موجود هستند که در ابتدا در پروپوزال اکوسیستم برنامه ریزی نشده بودند.

Troika

در انتهای دسامبر، الگوریتم هشینگ سبک و جدید Troika اعلام شد. اگرچه در طرح بودجه EDF گنجانده نشده بود اما پیاده سازی FPGA آن در دو نسخه توسعه پیدا کرد. یکی از آنها پیاده سازی سرعت بالا برای IOTA Crypto Core FPGA (یک سیکل ساعت در هر دور هشینگ) و دیگری یک نوع آهسته تر برای FPGA های ۵ دلاری بود. (تصویر پایین)

همچنین زمان زیادی به بهینه سازی پیاده سازی مرجع Troika اختصاص داده شد. اما در نهایت مشخص شد که فرد دیگری (بنام silent-hero) کار بهتری انجام داده است.

اما همچنین یک نسخه SIMD پیاده سازی شد که می تواند برای هشینگ هش های متعدد فورا مورد استفاده قرار گیرد. در نهایت مشخص خواهد شد که آیا آن هیچ استفاده ای دارد یا نه.

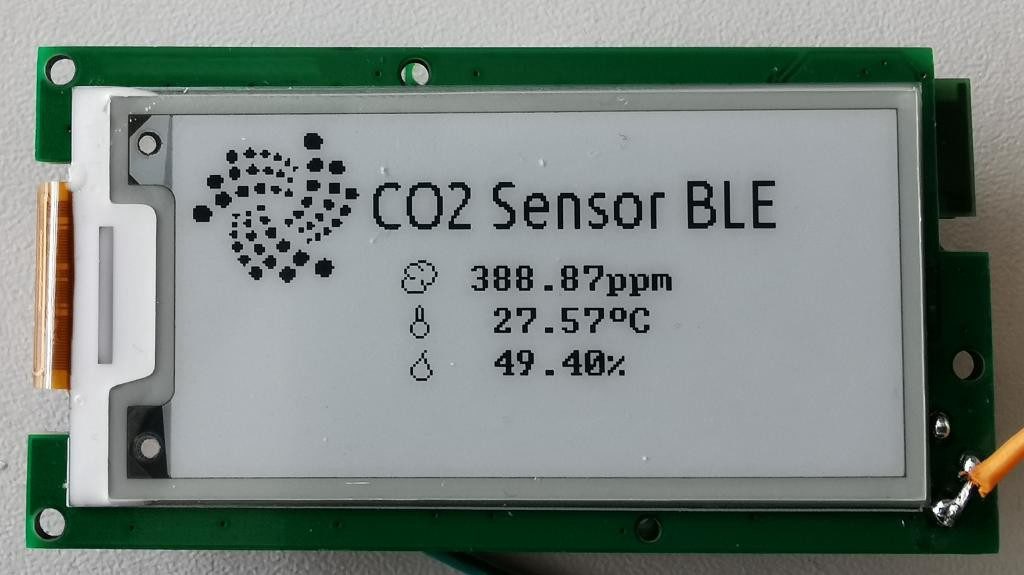

سنسور

بخشی که در پروپوزال EDF ذکر نشده بود یک سنسور می باشد. من یکی لازم داشتم و بنابراین آن را ساختم. من یک واحد nRF52، یک سنسور CO2 و یک نمایش E-Paper انتخاب کردم. چیز بسیار خوبی در مورد nRF52 این است که آنها می توانند مانند هر میکرو کنترل کننده بر اساس Cortex M دیگر برنامه نویسی شوند. بنابراین سنسور تنها به واحد UB1ox به عنوان پردازنده اصلی نیاز دارد و بلوتوث (BLE) به صورت رایگان همراه آن می باشد. من عاشق nRF52 هستم.

MAM

شاید شما متوجه شده اید، نمای معماری همیشه شامل MAM بوده است اما آن کم و بیش خارج شده بود. بخشی از این امر به این دلیل بود که MAM جدید آماده نبود و بخشی نیز به این دلیل بود که مشخص نبود که آیا MAM بر روی FPGA اجرا می شود و اگر اجرا می شود بر روی کدام بخش آن.

Cortex M1 منابع خیلی محدودی دارد. تنها در روز های آخر بود که سعی شد MAM بر روی واحد FPGA اجرا شود و به همین دلیل بود که اتمام پروژه سه روز به تاخیر افتاد.

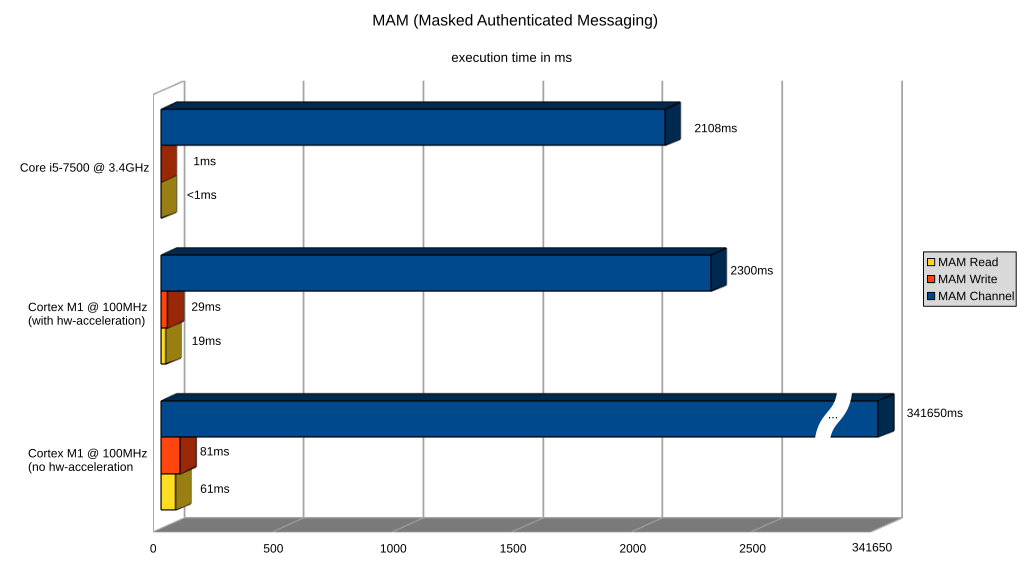

و البته آن کار کرد، این فقط یک گواه اثبات مفهوم است و توسعه زیادی را می توان انجام داد تا آن را آماده ساخت اما نشان می دهد که آن محتمل و بهترین است و آن به اندازه کافی سریع است تا استفاده کاربردی داشته باشد. MAM می تواند به مقدار زیاد از تسریع بخش Troika استفاده کند. در زیر مقایساتی با Cortex M1 با تسریع بخش سخت افزاری و بدون آن و یک سی پی یوی 3.4GHz i5 انجام شده است:

تسریع بخش سخت افزاری یک مزیت سرعت حدودا ۱۴۸ در مقایسه با یک پیاده سازی تنها نرم افزاری بر روی Cortex M1 را ارائه می دهد و می تواند تقریبا پا به پای i5 من حرکت کند، با کسری از قدرت (<۱W) و تنها ۱۰۰ مگاهرتز.

کار آینده

تا اینجا همگی کم و بیش کار گواه اثبات مفهوم بود و مشخص می شود که کدام بخش ها بیش از بخش های دیگر مورد استفاده قرار خواهند گرفت اما فکر می کنم که آن ماخذ خوبی برای توسعه بیشتر بدست دهد.

من خودم واحد FPGA را بیش از همه دوست دارم زیرا می تواند در اپلیکیشن های مستقل شبیه اینترنت اشیا خیلی به خوبی مورد استفاده قرار گیرد. آن مقدار زیادی قدرت هشینگ را فراهم می کند که برای آن معمولا یک کامپیوتر سی پی یو (PC CPU) مورد نیاز است اما تنها به کسری از قدرت نیاز دارد. آن آزادانه با زبان های C/C++ برنامه نویسی می شود و آن توسط مکانیسم های امنیتی محاسبه می شود. آن همچنین یک حافظه ایمن برای انبارش سید دارد. سیستم FPGA خیلی انعطاف پذیر است. اگر لوازم جانبی دیگر مورد نیاز باشد، سیستم بر طبق آن نیاز می تواند تغییر پیدا کند.

آنچه که به نظرم باید تغییر داده شود خلاص شدن از Cortex M1 soft-cpu و جایگزین کردن آن با RISC V رایگان می باشد. ARM وانمود می کند که Cortex M1 برای Xilinx FPGA ها رایگان است اما آن کاملا کاری در جهت پروانه دادن است (با دانلود از وبسایت ARM و منابع پچینگ بعد از آن).

مستند سازی

مستند سازی را می توان از طریق این لینک پیدا کرد. همه مخازن نیز از طریق این لینک قابل دسترسی هستند.

نتیجه گیری

من خوشحالم که همه چیز هایی که برنامه ریزی کرده بودم به خوبی انجام شد و مخصوصا این که در چارچوب های برنامه ریزی شده انجام گرفتند. مانند یک معجزه به نظر می رسد که اشتباهی برجسته روی نداد و موانع موجود نبودند. باید بگویم که شانس آوردم.

من از بنیاد آیوتا تشکر می کنم که به توانایی های من اعتماد کرد و این پروژه را با تامین وجه آن از طریق صندوق توسعه اکوسیستم (Ecosystem Development Fund) ممکن ساخت.